目錄微型電腦的硬體共性結構及基本性能指標關於存儲器的介紹微型電腦的基本性能指標1. 字長2. 主頻3. 存儲容量4. 外設擴展能力5. 軟體配置情況Arm Cortex 系列微處理器系列概述Arm Cortex-A 系列處理器Arm Cortex-R 系列處理器Arm Cortex-M 系列處理 ...

目錄

微型電腦的硬體共性結構及基本性能指標

微型電腦的硬體共性結構可以簡單地表述為:微型電腦是在內部集成了中央處理單元、存儲器(RAM/ROM 等)、定時器/計數器及多種 I/O 介面的比較完整的數字處理系統。

關於存儲器的介紹

隨機存取存儲器,也稱為主存(記憶體),是可以和 CPU 直接進行數據交換的內部存儲器,具有隨時讀寫、速度快的特點,一般用於存儲操作系統和其他正在運行的程式的臨時數據。 RAM 在使用的過程中可以從任意指定的地址進行寫入和讀出操作,但它的數據保護性不夠好,一旦斷電,其所存儲的數據就會消失。

Flash 存儲器具有不易失性、電擦除、可線上編程、存儲密度高、功耗低和成本低等特點。隨著 Flash 技術的逐步成熟, Flash 存儲器已經成為 MCU 的重要組成部分。 Flash 存儲器的不易失性與磁存儲器(MRAM)相似,不需要後備電源來保持數據。 Flash 存儲器可線上編程,可取代電擦除可編程只讀存儲器(EEPROM),用於保存運行過程中的參數。對 Flash 存儲器的讀寫不同於對一般 RAM 的讀寫,它需要專門的編程過程。 Flash編程的基本操作有兩種:擦除(Erase)和寫入(Program),擦除操作的含義是將存儲單元的內容由二進位的 0 變成 1,而寫入操作的含義是將存儲單元的某些位由二進位的 1變成 0。

微型電腦的基本性能指標

1. 字長

字長是電腦內部一次可以處理的二進位數的位數,一般電腦的字長取決於它的通用寄存器、記憶體儲器、 ALU 的位數和數據匯流排的寬度。目前,微型電腦的字長一般有 16 位、 32 位或 64 位。

2. 主頻

主頻是指微型電腦中 CPU 的時鐘頻率,也就是 CPU 運算時的工作頻率。一般來說,主頻越高,一個時鐘周期內完成的指令數越多,當然 CPU 的速度也就越快。目前 CPU 的主頻已達到 MHz、 GHz 級別。

3. 存儲容量

存儲容量是衡量微型電腦存儲能力的一個指標,它包括記憶體容量和外存容量。記憶體容量由 CPU 的地址匯流排的位數決定,目前已達到 MB、GB 級別;外存容量主要是指硬碟(Hard Disk)容量,目前已達到 GB、 TB 級別。

4. 外設擴展能力

一臺微型電腦可配置的外部設備的數量以及類型,對整個系統的性能有重大影響。如顯示器的解析度、多媒體介面功能和印表機型號等,都是外部設備選擇中要考慮的問題。

5. 軟體配置情況

軟體配置情況直接影響微型電腦系統的使用和性能的發揮,通常應配置的軟體有操作系統、電腦語言以及工具軟體等,另外還可配置資料庫管理系統和各種應用軟體。

Arm Cortex 系列微處理器系列概述

Arm Cortex-A 系列處理器

Arm Cortex-A 系列是基於 Arm v7A 架構基礎的處理器,面向尖端的基於虛擬記憶體的操作系統和用戶應用。作為開放式操作系統的高性能的應用程式處理器, 在高級工藝節點中可實現高達 2GHz 及以上標準頻率的卓越性能,從最新技術的移動 Internet 必備設備(如智能手機、移動計算平臺、 超便攜的上網電腦或智能電腦等)到汽車信息娛樂系統、 企業網路、印表機、伺服器和下一代數字電視系統無處不在。 因而 Arm Cortex-A 系列處理器適用於具有高計算要求、運行豐富操作系統以及提供交互媒體和圖形體驗的應用領域。

Arm Cortex-R 系列處理器

Arm Cortex-R 系列是基於 Arm v7R 架構基礎的處理器,面向實時系統的應用, 為具有嚴格的實時響應限制的嵌入式系統提供高性能計算解決方案。目標應用包括智能手機、硬碟驅動器、數字電視、醫療行業、工業控制、汽車電子等。 Arm Cortex-R 處理器是專為高性能、可靠性和容錯能力而設計的,其行為具有高確定性,同時保持很高的能效和成本效益。

Arm Cortex-M 系列處理器

Arm Cortex-M 系列是基於 Arm v7M/v6M 架構基礎的處理器,面向微控制器的應用, 是一系列可向上相容的高能效、易於使用的處理器,這些處理器旨在幫助開發人員滿足將來的嵌入式應用的需要。 Arm Cortex-M 系列針對成本、 功耗敏感的 MCU 和終端應用(如智能測量、 人機介面設備、汽車和工業控制系統、大型家用電器、消費性產品和醫療器械等)的混合信號設備進行優化。

Cortex-M3 和 Cortex-M4簡介

處理器類型

ARM Cortex-M 為 32 位 RISC(精簡指令集)處理器,其具有

- 32 位寄存器

- 32 位內部數據通路

- 32 位匯流排介面

Cortex-M3 和Cortex-M4 處理器都具有三級流水線(取指、解碼和執行),它們都基於哈佛匯流排架構,取指令和數據訪問可以同時執行。

ARM Cortex-M 處理器的存儲器系統使用 32 位定址,地址空間最大為 4GB。存儲器映射是一致的,這就意味著儘管匯流排介面有多個,4GB存儲器空間卻只有一個。存儲器空間包括程式代碼、數據、外設以及處理器內的調試支持部件。

與其他任何 ARM 處理器相同,Cortex-M 處理器基於一種載入—存儲架構。這也就意味著數據需要從存儲器中載入和處理後,使用多個單獨的指令寫回存儲器。例如, 要增加 SRAM 中存儲的數據值,處理器需要使用一條指令從 SRAM 中讀出數據,並且將數據放到處理器的寄存器中,然後使用第二條指令增加寄存器中的數據值,最後使用第三條指令將數值寫回存儲器。處理器內部的寄存器細節一般被稱作編程模型。

架構

對於ARM處理器,架構一般指兩個方面:

- 架構:指令集架構(ISA)、編程模型(對軟體可見)以及調試方法(對調試器可見)

- 微架構:介面信號、指令執行時序以及流水線階段等實現相關的細節,微架構為處理器設計相關的。

Cortex-M3 和Cortex-M4 處理器都基於ARMv7-M 架構。

指令集

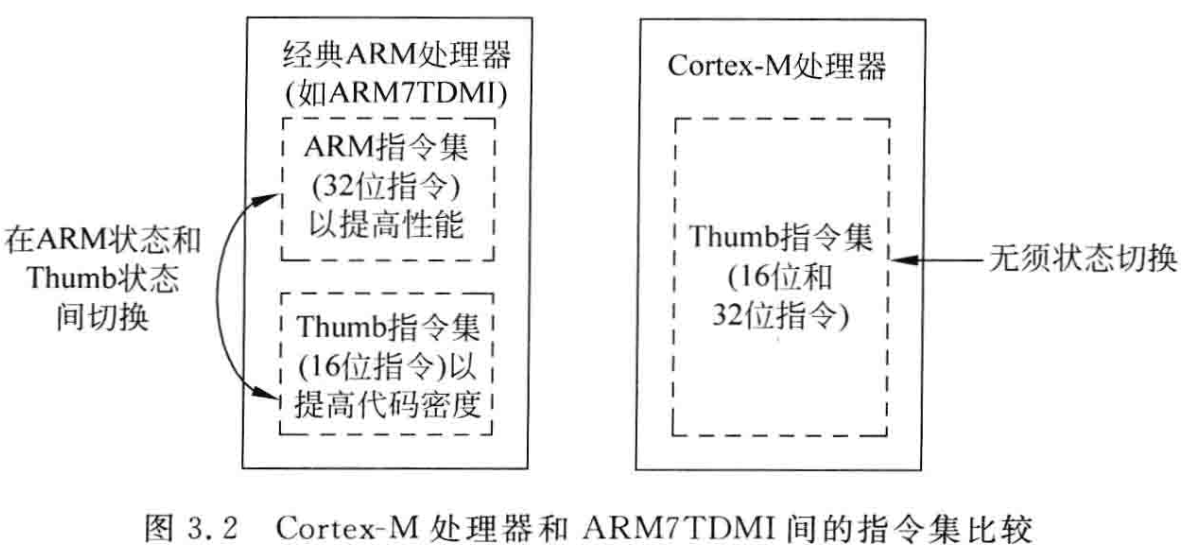

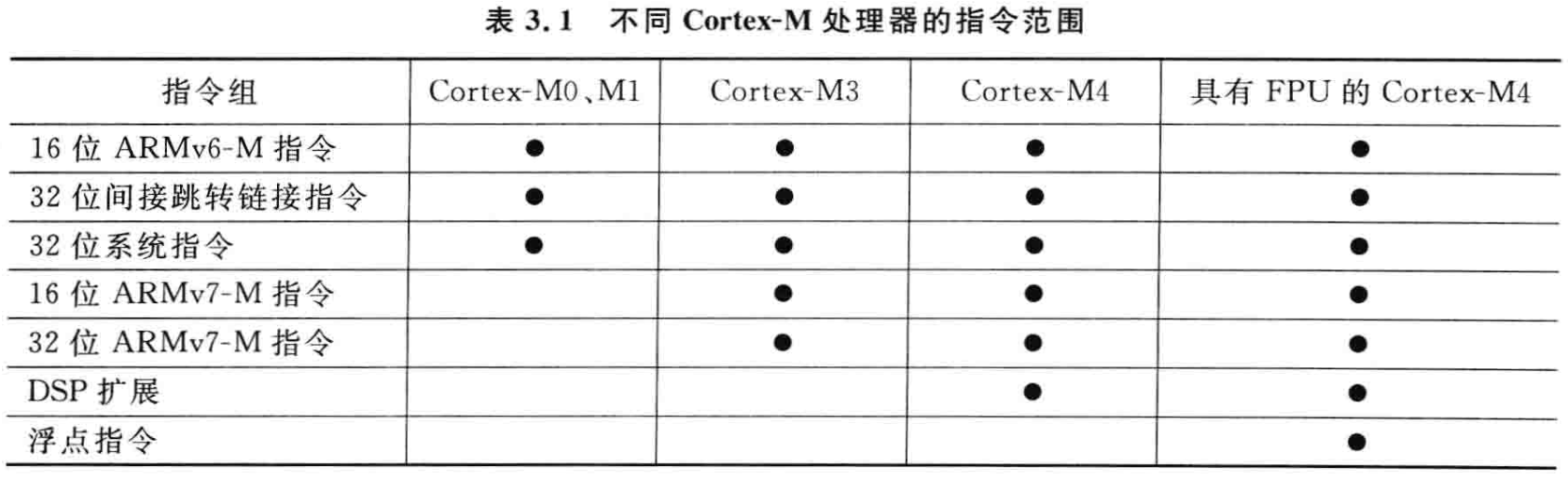

Cortex-M 處理器使用的指令集名為 Thumb(其中包括 16 位 Thumb 指令和更新的 32 位 Thumb 指令),Cortex-M3 和 Cortex-M4 處理器用到了 Thumb-2 技術,它允許 16 位和 32 位指令的混合使用,以獲取更高的代碼密度和效率。

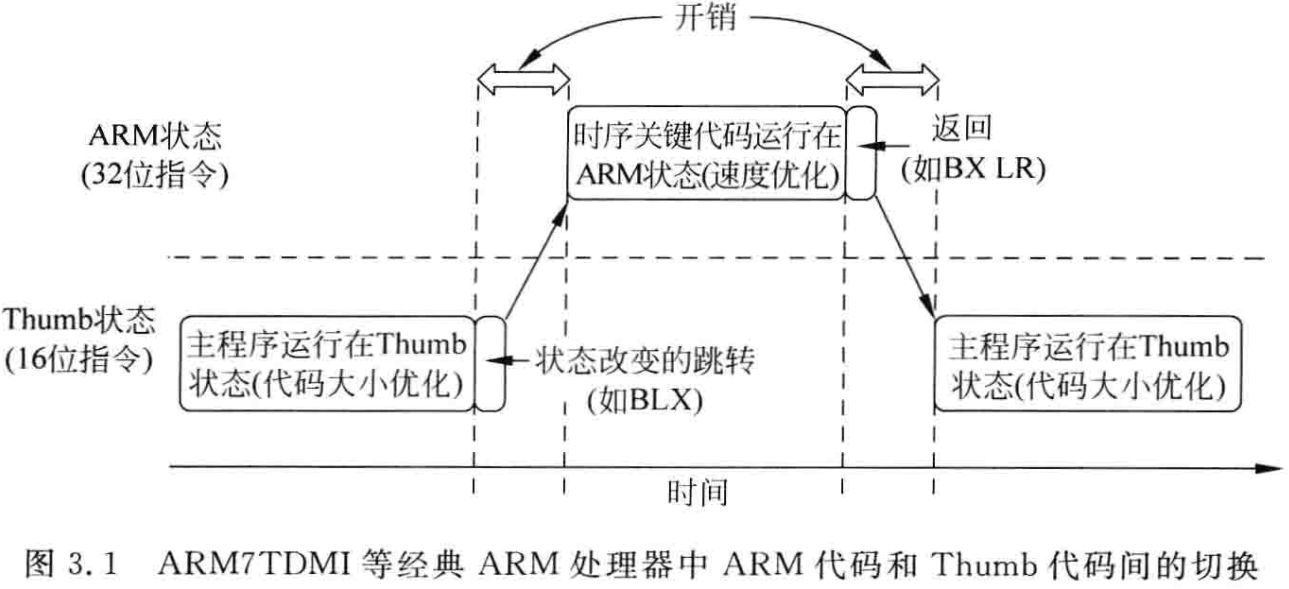

經典的 ARM 處理器:具有兩種操作狀態 32 位的 ARM 狀態和 16 位的 Thumb 狀態。在 ARM 狀態中,指令是 32 位的,內核能夠以很高的性能執行所有支持的指令;而對於 Thumb 狀態,指令是 16 位的,這樣可以得到很好的代碼密度,不過 Thumb 指令卻不具有ARM指令的所有功能,要完成特定的操作,可能需要更多的指令。中斷處理是會進人 ARM 狀態的。

要同時得到兩者的優勢,許多用於經典ARM處理器的應用程式混合使用了 ARM 和 Thumb 代碼。不過這種混合編碼的方式並不是非常理想,它會帶來狀態間切換的開銷(執行時間和指令數),而且兩個狀態的分離還增加了軟體編譯過程的複雜度,對於不是很熟練的開發人員來說,優化代碼更加困難。

Thumb-2 技術:Thumb 指令被擴展為支持 16 位和 32 位兩種解碼方式,無須在兩個不同操作狀態間切換就可以滿足所有的處理需求。Cortex-M 處理器根本不支持 32 位的 ARM 指令,甚至中斷處理都可以完全在 Thumb 狀態中實現。

經典的 ARM 處理器相比,Cortex-M 處理器(Thumb-2 技術)優勢:

- 無狀態切換開銷,節省執行時間和指令空間。

- 無須指定源文件中的 ARM 狀態或 Thumb 狀態,開發軟體也更容易

- 在獲得最佳的代碼密度和效率的同時,還能很容易地達到高性能

- 利用 Thumb-2 技術,與 ARM 經典處理器相比,Thumb 指令集已經得到很大的擴展。註意,儘管所有的Cortex-M處理器都支持 Thumb-2 技術,它們實現的 Thumb ISA 子集不盡相同。

模塊框圖

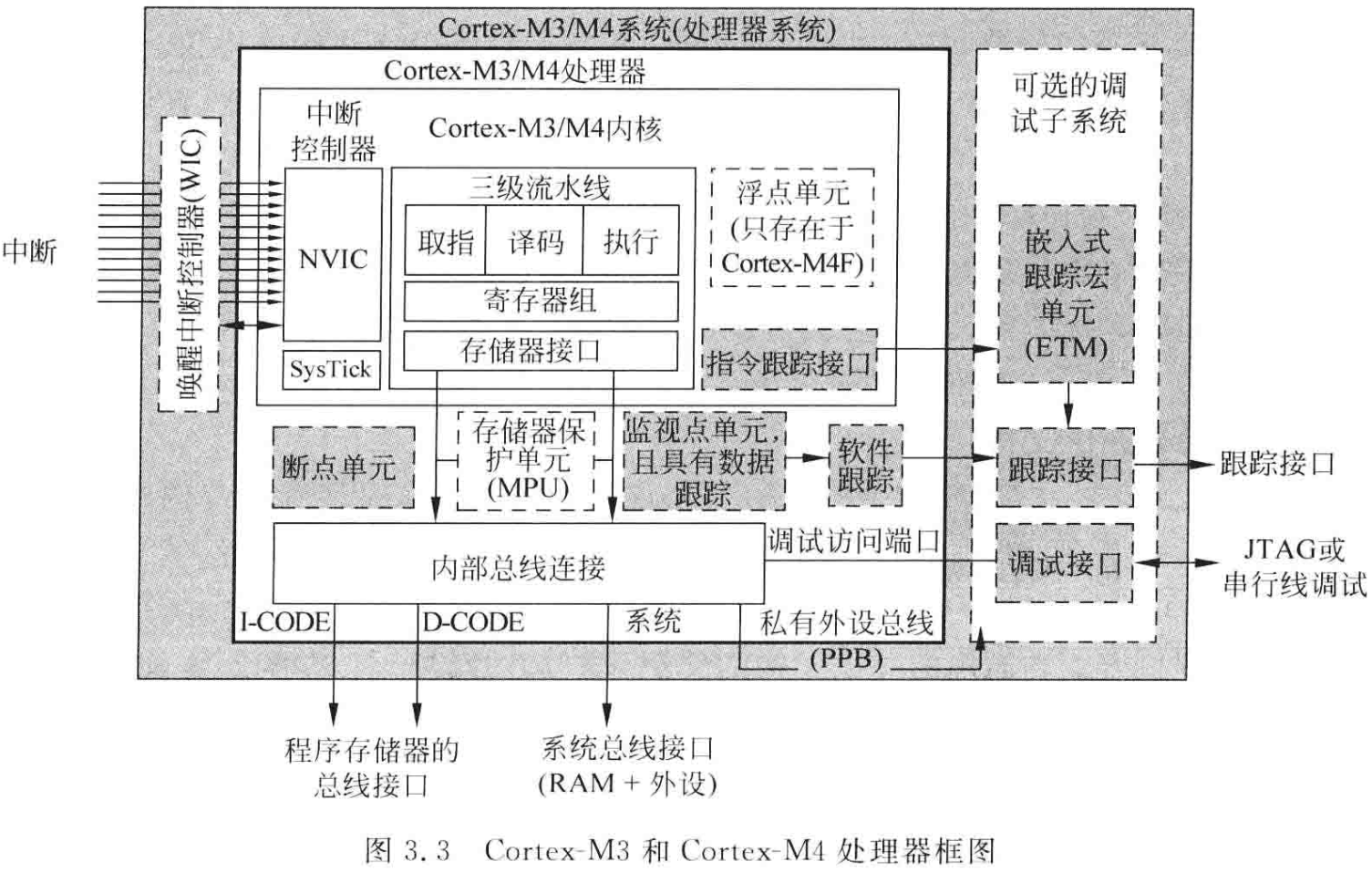

從較高的層級來看,Cortex-M3 和 Cortex-M4 是非常相似的。儘管它們在內部數據通路設計上存在巨大差異,處理器的一些部分還是相似的,如取指緩衝、部分指令解碼和執行階段以及 NVIC。另外,“內核”層級外的部件基本上是相同的。Cortex-M3 和 Cortex-M4 處理器包含處理器內核、嵌套向量中斷控制器(NVIC)、SysTick定時器以及可選的浮點單元(用於 Cortex-M4)。除了這些以外,處理器中還有一些內部匯流排系統、可選的存儲器保護單元(MPU)以及支持軟體調試操作的一組部件。內部匯流排連接可以將處理器和調試產生的傳輸送到設計的各個部分。

Cortex-M3 和 Cortex-M4 處理器是高度可配置的。例如,調試特性是可選的,若產品需要支持調試,片上系統設計人員可以將調試部件去掉,這樣可以顯著降低設計的矽片面積。有些情況下,晶元設計人員還可以選擇降低硬體指令斷點和數據監視點比較器的數量,以降低系統的門數量。許多系統特性也是可配置的,如中斷輸入的數量、支持的中斷優先順序的數量以及 MPU 等。

存儲器系統

Cortex-M3 和 Cortex-M4 處理器本身並不包含存儲器(沒有程式存儲器、SRAM或緩存),它們具有通用的片上匯流排介面,因此,微控制器供應商可以將它們自己的存儲器系統添加到系統中。一般來說,微控制器供應商需要將下麵的部件添加到存儲器系統中:

- 程式存儲器,一般是 Fash。

- 數據存儲器,一般是 SRAM。

- 外設。

這樣,不同微控制器產品可能會具有不同的存儲器配置、不同的存儲器大小和類型,以及不同的外設。

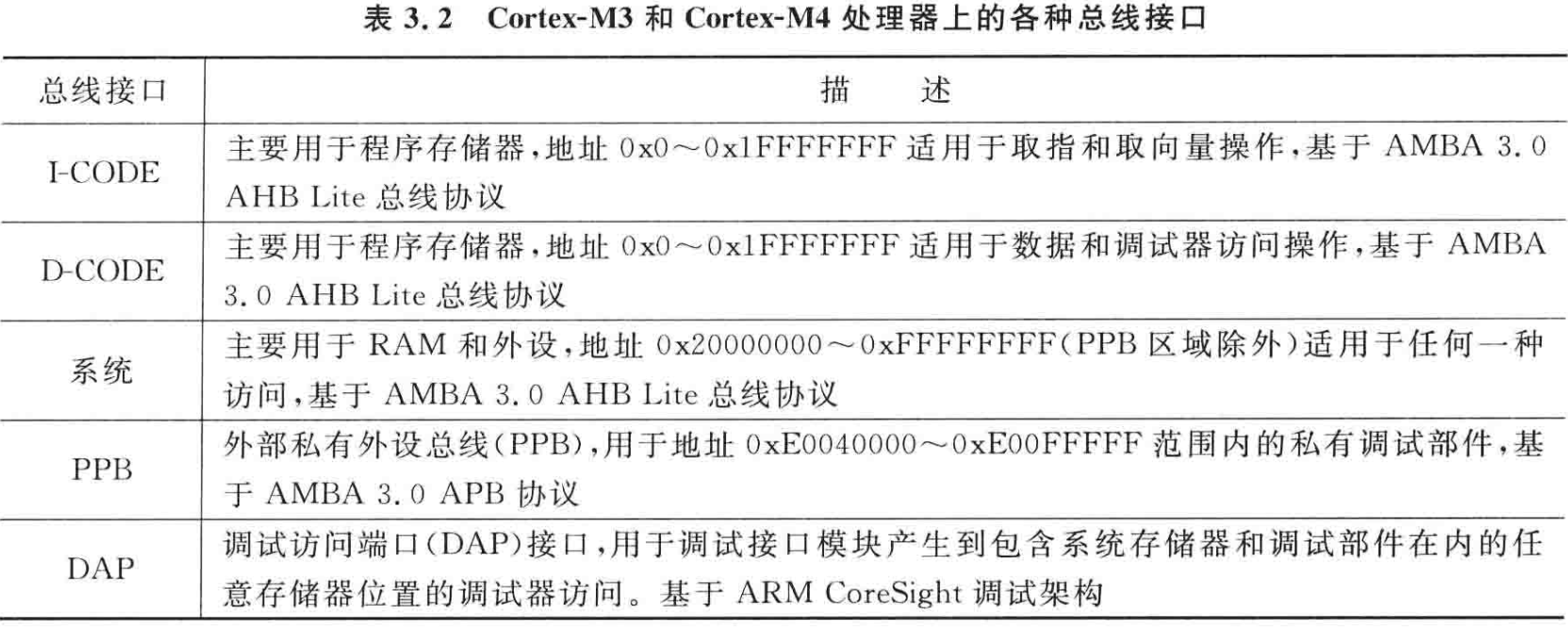

Cortex-M 處理器的匯流排介面為 32 位寬,且基於高級微控制器匯流排架構(AMBA)標準。AMBA 中包含多個匯流排協議,任何晶元設計者都可以免費使用這些標準協議。AMBA 規範可以從 ARM 網站下載。由於這些標準協議的低硬體成本、效率以及開放性,它們大受晶元設計者的歡迎。

Cortex-M3 和 Cortex-M4 處理器主要使用的匯流排介面協議為 AHBLite(高級高性能匯流排),它用於程式存儲器和系統匯流排介面。AHBlite 協議為流水線結構的匯流排協議,可以在低硬體成本下實現高運行頻率。高級外設匯流排(APB)介面為處理器使用的另外一種匯流排協議,它通常用於基於ARM的微控制器的匯流排系統。另外,APB協議在Cortx-M3和Cortex-M4處理器內部還用於調試支持。

與片外匯流排協議不同,AHBLite 和 APB 協議相對簡單。這是因為晶元內的硬體配置是固定的,無須一種複雜的初始化協議來處理可能的配置(例如,無須支持類似於電腦技術中的“熱插拔”)。

中斷和異常支持

Cortex-M3 和 Cortex-M4 處理器中存在一個名為嵌套向量中斷控制器(NVIC)的中斷控制器,它是可編程的且其寄存器經過了存儲器映射。NVIC 的地址固定,而且 NVIC 的編程模型對於所有的 Cortex-M 處理器都是一致的。

除了外設和其他外部輸入的中斷外,NVIC 還支持多個系統異常,其中,包括不可屏蔽中斷(NMI)和處理器內部的其他異常源。

Cortex-M3 和Cortex-M4 處理器是可配置的,微控制器供應商能夠決定 NVIC 設計實際支持的可編程中斷優先順序的數量。儘管 NVIC的一些細節在不同的 Cortex-M3/M4 處理器間可能存在差異,中斷/異常的處理和 NVIC 的異常模型卻是相同的,它們定義在架構參考手冊中。